Design of BCMO4 Bluetooth Communication Module Based on NIOS II

Design of BCMO4 Bluetooth Communication Module Based on NIOS II

This design uses the second-generation low-cost FPGA chip developed by Altera Corporation, on which the NIOSâ…¡ Bluetooth communication module based on BCM04 is developed. The communication module can replace the cable and be effectively applied to the industrial site with complex and changeable working environment, and can realize wireless communication with field devices, access points, handheld devices and other devices.

Introduction In the industrial scene, most communication equipment is realized by adding communication modules, and most of the communication module processors use ARM cores. With the rapid development of microelectronics and computer science, electronic systems have evolved from board-level system integration to multiple modes including ASIC, FPGA and embedded systems. SOPC, due to the integration of hard or soft core CPU, DSP, memory, peripheral I / O and programmable logic modules, has greater advantages in terms of design, due flexibility and cost.

The NIOS II series processors are Altera's second-generation FPGA embedded processors. Compared with the previous-generation soft-core CPU, the performance of NIOS II has been greatly improved, the volume is smaller, and its maximum processing capacity is three times that of the first-generation soft core. The logic function has a 32-bit reduced instruction set CPU. The implementation method is realized by programming on the FPGA, which is a fundamental difference from the traditional CPU. In this paper, the Bluetooth communication module is designed on the basis of the NIOSâ…¡ soft core, and in industrial Ethernet, the wireless communication between the communication module and the industrial field device is better achieved.

Overview of NIOSâ…¡ Embedded Processor

The NIOSâ…¡ processor is Altera's second-generation user-configurable general-purpose 32-bit RSIC soft-core microprocessor. It is Altera's unique soft CPU core based on a general-purpose FPGA architecture. It can provide: complete 32-bit instruction set, data bus and address space; 32-bit general purpose register; 32 external interrupt sources; special instructions for calculating 64-bit and 128-bit products; single-instruction barrel shifter; On-chip peripherals are accessed to provide off-chip memory and peripheral interfaces; under IDE control, a hardware-assisted debugging module can start, stop, single-step, and trace operations on the processor; based on the CNU C / C ++ tool chain and Eclipse IDE ; All NIOSâ…¡ processor systems are compatible with the instruction set; have a performance of more than 150 DMIPS.

It integrates design input, synthesis, layout, verification, programming and configuration, and third-party EDA tool interfaces into a seamless and comprehensive design environment. The hardware development environment of NIOSâ…¡ is carried out in SOPC builder. SOPC builder is an automated SOPC hardware system development tool, integrated in Quartus II software. Quartus II and SOPC builder together provide a standardized graphical environment for establishing SOPC designs. Quartus â…¡ and SOPC builder software can define a complete hardware system in a short time. SOPC builder shortens the time to market of products through the automation of system definition, integration, and verification at the SOPC development stage.

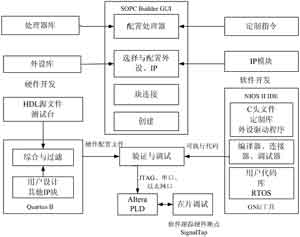

The NIOSâ…¡ software development environment is called the NIOSâ…¡ Integrated Development Environment (IDE). It is embedded in the Quartus II design tool, and the application program can be downloaded to the SOPC hardware system for debugging through JTAG, and the application program can be simulated and debugged in the instruction set simulator, or can be simulated and debugged in the ModelSim software. The soft and hard development environment and design flow of SOPC based on NIOSâ…¡ are shown in Figure 1.

Figure 1 SOPC software and hardware development environment and process based on NIOSâ…¡

First use the interface of SOPC Builder to customize the system and generate output files; then enter the traditional FPGA hardware development process; perform logic synthesis, place and route in Quartus II. In the software process, users use the NIOSâ…¡ IDE environment to build projects, compile designs, and debug.

Bluetooth communication module hardware design Bluetooth technology is an open, short-range wireless communication technology standard, working in the global 2.4GHz ISM band, using frequency hopping spread spectrum technology, can be used to achieve close-range wireless connection through fixed The network interconnection between devices and mobile devices realizes flexible, safe, low-cost, and low-power data and voice communication between various digital devices, and realizes a full range of data transmission.

There are a variety of devices that use different methods for interconnection in industrial sites. For some harsh environments, inconvenient wiring and other factors can use Bluetooth wireless communication technology to achieve data communication. In this design, the FPGA chip EP1C12Q240C8 based on the NIOSâ…¡ soft core is used as the CPU processor, and the 64Mb SDRAM and 16Mb Flash are expanded on the periphery of the processor. Module, in order to realize the communication protocol in the Bluetooth communication module and send test data or receive control commands through the Bluetooth module. Figure 2 is a hardware design block diagram of a Bluetooth communication module based on the NIOS II soft core.

Figure 2 Hardware design block diagram of Bluetooth communication module based on NIOSâ…¡ soft core

The Flash of AM29LV160 and SDRAM of HY57V461620 are used in the communication module. The storage capacity of the CPU has been expanded to ensure the transplantation of communication protocols and operating systems (Linux, Windows CE) on the EPA network. The reset circuit is composed of a 10kΩ resistor, a 10μF capacitor and a button, which can realize the low-level reset of the button and the low-level reset of the power-on.

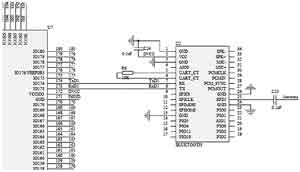

The realization of the Bluetooth module adopts the single chip BCM04 of CSR company. BCM04 is embedded with BlueCore04 chip, and provides SPI, UART / USB, PIO, PCM interfaces. BCM04 comes with 8Mb flash memory SST39VF800, operating voltage is 2.7 ~ 3.6V. Connect the balun between the antenna and the output of the transmitter. The band-pass filter is generally a passive device, and its role is to filter out signals in the frequency band that the receiver does not need, and to provide selective signals for the low-noise amplifier (LNA) to reduce interference. BCM04 adopts Taiwan ACX's integrated band-pass filter + balanced unbalanced converter device FB2520. The band-pass filter and balanced-unbalanced converter are integrated together to achieve higher integration and effectively reduce the circuit board area , The device has the advantages of small size, low insertion loss, etc., and can well complete the function of conversion from balanced to unbalanced and band-pass filtering. Two voltages of 3.3V and 1.5V are required in BCM04, of which 1.5V is used to power the Bluetooth chip and bandpass filter + balanced-unbalanced converter, and 3.3V provides voltage for the peripheral I / O pins of the Flash chip and Bluetooth chip. The circuit diagram of the interface between the CPU and the Bluetooth module is shown in Figure 3.

Figure 3 Circuit diagram of CPU and Bluetooth interface

SOPC Design of FPGA Chip Based on NIOSâ…¡ Soft Core

The NIOSâ…¡ embedded processor is a soft-core CPU introduced by FPGA manufacturer Altera Corporation. It is a general-purpose RISC (reduced instruction set architecture) embedded CPU that can be customized flexibly for users. NIOSâ…¡ is provided to users in soft core mode, and is optimized for FPGA implementation on Altera, used for SOPC integration, and finally implemented on FPGA. In order to complete the design requirements, the processor chip needs to be configured. The configuration on its SOPC Builder is shown in Figure 4.

Figure 4 Bluetooth communication module configuration diagram on SOPC Builder

SOPC design includes embedded hardware configuration, hardware design, hardware simulation, software design and software debugging, etc. with 32-bit NIOS II soft core processor as the core. The CPU, memory interface (FLASH and SDRAM), standard peripheral interface (Bluetooth interface), three-state bridge, hardware and software program download port and timer are defined in SOPC Builder.

Software design The software design of the Bluetooth communication module mainly focuses on the driver development of the NIOS â…¡ soft core and the conversion of the Bluetooth protocol. Altera provides character mode devices, timer devices, file subsystems, Ethernet devices, DMA devices, and Flash devices in the hardware abstraction layer, and provides a series of unified initialization and access function interfaces for each device. Through the reading and writing of these interfaces, the driver development of the NIOS II soft core can be completed.

First initialize the Bluetooth module. The Bluetooth module does not work after loading various protocol layers, and the initial parameters of the module need to be set according to different hardware designs. The initial parameter setting is also called PSK setting, which can be achieved through the BlueLAB integrated development environment or PS Key setting software. Figure 5 shows the PS Key setting interface.

Figure 5 PS Key setting interface

The Bluetooth protocol stack has been solidified in the Bluetooth chip, so after the Bluetooth module is initialized, the Bluetooth module can be used to read and write other wireless devices on the industrial site and update the Bluetooth instructions. The following program is to implement all function pointers of Bluetooth serial port driver.

typedef struct _HW_VTBL {

PVOID (* HWInit) (ULONG IdenTIfier, PVOID pMDDCon-text, PHWOBJ pHWObj);

BOOL (* HWIoct1) (PVOID pHead, DWORD dwCode,

PBYTE pBufIn, DWORD dwLenIn, PBYTE pBufOut, DWORD

DwLenOut, PDWORDpdwActualOut);

} HW_VTBL, * PHW_VTBL;

// Define the name of the Bluetooth simulation serial port DDSI function.

Const HW_VTBL BluetoothVTbl = {

BluetoothInitSerial,

BluetoothIoctl

};

// The structure variable CTRLVTbl defines the list of DDSI function names of the control port

Const HW_VTBL CTRLVTbl = {

CTRLInitSerial,

CTRLDeinit,

CTRLOpen,

CTRLClose,

CTRLIoctl

};

Summary Bluetooth technology is an open global specification for wireless data and voice communication. It is based on low-cost, close-range wireless connections and establishes a specially connected short-range wireless technology for the communication environment of fixed and mobile communication devices. Bluetooth technology has the characteristics of low consumption, low power consumption and high security. This design is based on Bluetooth technology, combined with a CPU embedded in NIOS II soft core, using SOPC technology, which can be cut, expanded, and upgraded, and has the function of software and hardware programmable in the system. The use of FPGA chip in the Bluetooth communication module makes it possible for the communication module to change the configuration of the CPU according to the actual needs of the industrial site, which is convenient for future hardware and software upgrades of the system and extends the service life of the communication module. The environment provides a guarantee.

This Car LED Light is IP56 waterproof rating, which could better protect the LED Bulb from the water or harsh environment. Energy Saving LED Light Bar could not only used in RV but also could use in many other application of Marine, Truck, Camper, motor home, Limousine, Travel trailer, caravan, boat etc.

There are 12V DC 24VDC Voltage could be choose from. The Emitting Color could choose, including Red, White, Blue and etc. The Working life of the Ceiling Light is 30,000 Hours, which is a long time for use.

LED Light

LED Light,Car LED Light,RV Light,LED Lamp

YESWITCH ELECTRONICS CO., LTD. , https://www.yeswitches.com